はじめに

自己紹介

十年間にわたり組込みOSの分野でFAE/プロジェクトマネージャを経験。

現在はヘテロマルチコア向けのソースコード解析や最適化を行うSilexicaで奮闘中。

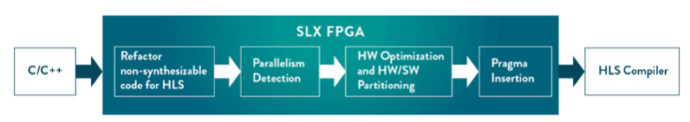

HLSの一般的なユースケースは、サードパーティーによって生成されたもの、あるいは既存のC/C++アルゴリズムをHLSコンパイラを使用してハードウェア実装に変換します。しかし、基礎となるコードについての洞察や理解がほとんどない場合、開発者に多くの課題を与える可能性があります。 SLX FPGAは、開発者がHLSのアルゴリズムコードを理解し最適化のサポートをすることによって、これらの課題に対する解決策を提供します。

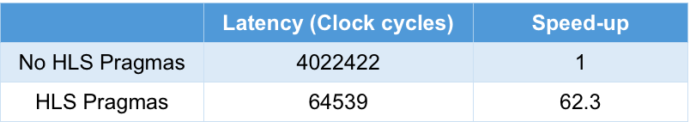

最近発表されたホワイトペーパーでは、SLXFPGAを用いてMATLAB Embedded Coder™で生成されたC/C+アルゴリズム(この場合はカルマンフィルター)を使用し、HLS用にC/C++ コードを最適化する方法について解説されています。この例では、プラグマが挿入されていない元のコードに対してHLSコンパイラによって生成されたソリューションと比較し、SLX FPGAがHLSプラグマを自動挿入したコードのほうがパフォーマンスが62倍以上も改善されました。

ホワイトペーパーでは、以下の設計フロー手順について詳しく説明します。

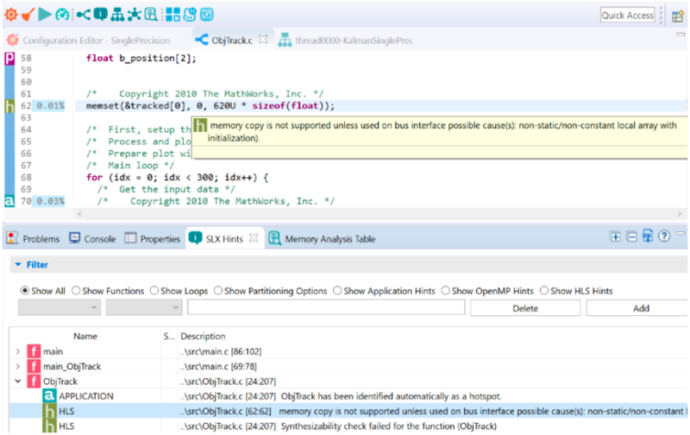

HLS用の合成不可能なコードのリファクタリング

MATLAB Embedded CoderでアルゴリズムC/C++コードを生成した後、SLX FPGAはHLSコンパイラによって合成不可能なコードを識別し、コードをHLS合成可能なコードに変換するための自動およびガイド付きコードリファクタリングを提供します。

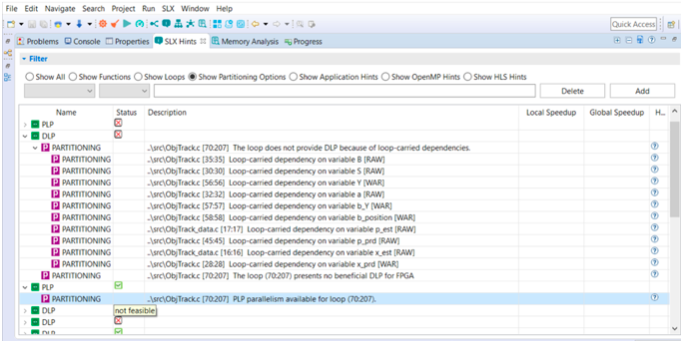

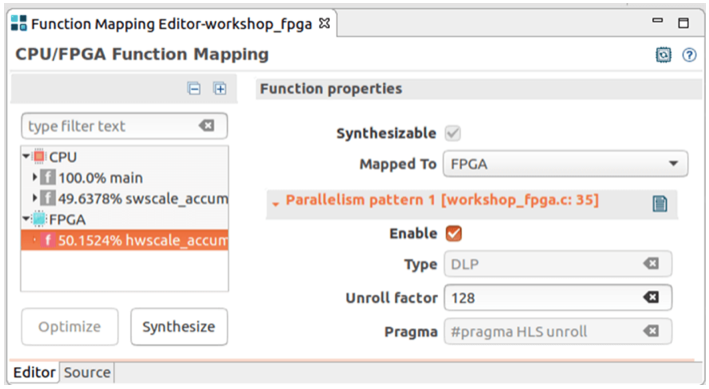

並列処理の検出

SLX FPGAは並列処理を検出し、ハードウェア実装でどのように活用するかを開発者にガイドします。 また、並列処理の障害をフラグで示し、ユーザーがそれらの障害を排除することを助け、追加の並列処理を行えるようにします。

ハードウェアの最適化

SLX FPGAは、適切な関数のパイプライン化とループの展開を調査し、ターゲットプラットフォームで使用可能な配列分割と利用可能なインターフェースのデザインスペースを通じてハードウェアにデータを提供します。

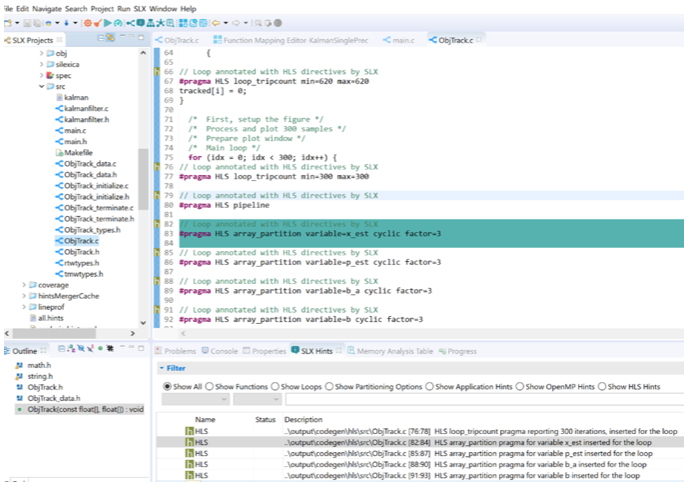

プラグマ挿入

SLX FPGAは、コンパイラの最適化を導くHLSプラグマを自動的に挿入します。また、 HLSプラグマには、チューニングが必要な様々なパラメータが含まれています。 SLX FPGAは、静的および動的解析データを活用し、最適化アルゴリズムと組み合わせることとで、開発者が提供する制約に基づいて調整および最適化されたプラグマを挿入します。

SLXとVivado HLSを使用してMATLAB Embeddedコーダーによって生成されたアルゴリズムをFPGAに実装する方法に関しては、ホワイトペーパー「MATLABで生成C / C ++からの高位合成の加速」をダウンロードしてください。ライブデモ、またSLX FPGAの評価を検討したい場合は、こちらからお問い合わせください。